IDEa

From Atariki

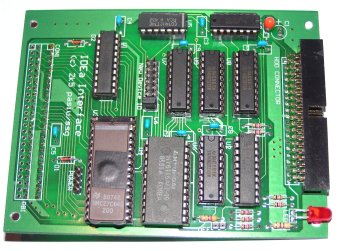

Pasiowa wersja interfejsu KMK/JŻ IDE.

Spis treści |

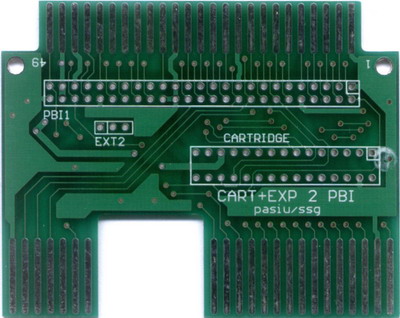

Wygląd pcb kontrolera oraz przelotki

Kontroler można bez przeszkód zamontować w środku komputera. Polecanym miejscem jest przestrzeń nad modulatorem, złączem IDE w stronę portu SIO.

dla przypomnienia :

- Freddie (CO61922 lub CO61991)

- MMU (CO61618)

- 6502C (CO14806) - CPU - na nim znajdziemy większość sygnałów

- Antic (CO21698)

Poszczególne piny interfejsu należy połączyć przewodami (jak najkrótszymi) z:

- pin1 [con1]- GND - srebrna ścieżka krawędziowa (wystarczy podłączyć tylko raz, mimo iż GND jest też na innych pinach)

- pin2 - EXTSEL - 3 pin Freddiego (w przypadku XEGS oraz 65xe bez EXP należy wylutować wspomnianą nóżkę z płyty głównej oraz podłączyć ją do zasilania przez opornik 4,5-10k)

- pin3 - A0 - 9 pin CPU

- pin4 - A1 - 10 pin CPU

- pin5 - A2 - 11 pin CPU

- pin6 - A3 - 12 pin CPU

- pin7 - A4 - 13 pin CPU

- pin8 - A5 - 14 pin CPU

- pin9 - A6 - 15 pin CPU

- pin10 - GND

- pin11 - A7 - 16 pin CPU

- pin12 - A8 - 17 pin CPU

- pin13 - A9 - 18 pin CPU

- pin14 - A10 - 19 pin CPU

- pin15 - A11 - 20 pin CPU

- pin16 - A12 - 22 pin CPU

- pin17 - A13 - 23 pin CPU

- pin18 - A14 - 24 pin CPU

- pin19 - GND

- pin20 - A15 - 25 pin CPU

- pin21 - D0 - 33 pin CPU

- pin22 - D1 - 32 pin CPU

- pin23 - D2 - 31 pin CPU

- pin24 - D3 - 30 pin CPU

- pin25 - D4 - 29 pin CPU

- pin26 - D5 - 28 pin CPU

- pin27 - D6 - 27 pin CPU

- pin28 - D7 - 26 pin CPU

- pin29 - GND

- pin30 - GND

- pin31 - Ø2 - pin 29 ANTICA

- pin32 - GND

- pin33 - ****

- pin34 - RST - 36 pin ANTICA

- pin35 - ****

- pin36 - ****

- pin37 - ****

- pin38 - ****

- pin39 - ****

- pin40 - ****

- pin41 - ****

- pin42 - GND

- pin43 - MPD - 14 pin MMU ( !!! UWAGA - XEGS - komentarz poniżej )

- pin44 - ****

- pin45 - GND

- pin46 - R/W: Read/write direction - 14 pin ANTICA

- pin47 - VCC ( zasilanie - np. 8 pin CPU)

- pin48 - VCC

- pin49 - ****

- pin50 - GND

W przypadku ATARI XEGS konieczne jest zastąpienie oryginalnego MMU GALEM16V8 zaprogramowanym plikiem *.jed autorstwa PASIA/SSG. Po tej operacji sygnał MPD jest na pinie 13. Po wymianie MMU odginamy ww. nóżkę do poziomu i podłączamy do niej 5V przez opornik z zakresu 4,7-10K.

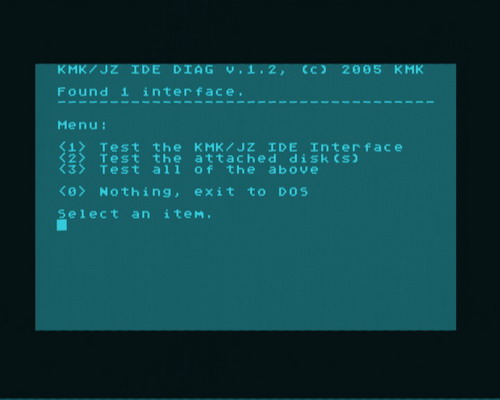

- TIP: za długie kable mogą być przyczyna przekłamań w programie KMKDIAG !!!

- TIP2: sygnały A0-A15 i D0 podane powyżej są nie tylko na CPU. Wystarczy spojrzeć na rozpiskę pinów ANTICA,GTIA, Pokeya

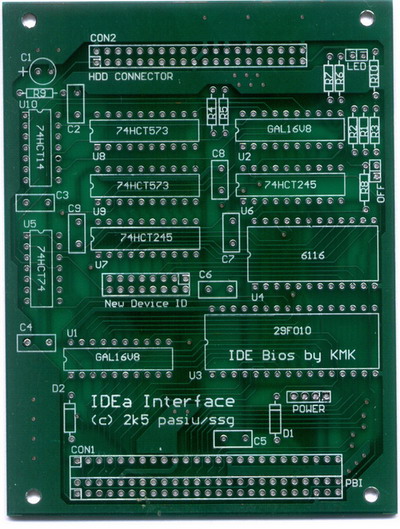

Wykaz elementów elektronicznych układu

Układy scalone

- U01 - GAL 16v8 o czasie propagacji 15ns, najlepiej 25ns, zaprogramowany IDEaBios.jed

- U02 - GAL 16v8 o czasie propagacji 15ns, najlepiej 25ns, zaprogramowany IDEaReg2.jed

- U03 - Flash 29f010 o czasie max 200ns

- U04 - 6116 czas dostępu max 150ns

- U05 - 74hct74

- U06 - 74hct245

- U07 - 74ls245

- U08 - 74hct573

- U09 - 74hct573

- U10 - 74hct14

Elementy bierne

- C1 - 2.2uF

- C2-C9 - 100nF

- R01-R07 - 33

- R08 - 4,7k

- R09 - 4.7K

- R10 - 330

- D1, D2 - Bat42

- D3 - 1 Led

Wykryte błędy

Błędy oznaczeń PCB

PCB zawiera jeden błąd w miejscu R9 wlutowujemy kondensator C1 (+ od strony C2) a w miejsce C1 rezystor R9.

Uaktualnienie do IDEa rev. B

Należy przeciąć ścieżkę idącą od 2 pinu układu U5 74HCT74 biegnącą do 6 pinu układu U6 74HCT245 i połączyć przewodem 2 pin układu u5 74HCT74 z 3 pinem układu U4 6116.

Ta mała modyfikacja usunie jeden mały błąd - objawiający się zwisem podczas próby wyjścia z programu KMKDIAG (w oryginale - IDEa rev. A - rejestry bankujące pamięć wewnętrzną zamienione są omyłkowo miejscami).

Uaktualnienie do IDEa rev. C

Poprawa stabilności interfejsu z wieloma egzemplarzami Atari. W celu poznania szczegółów należy skontaktować się z Candle'em.

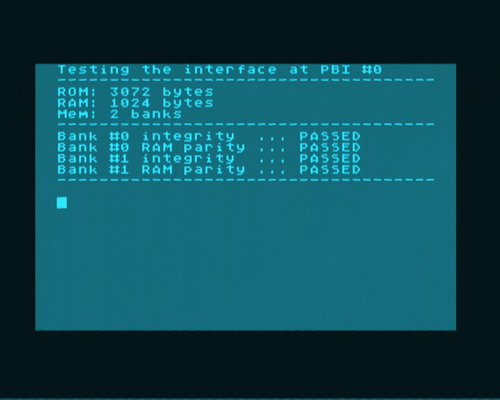

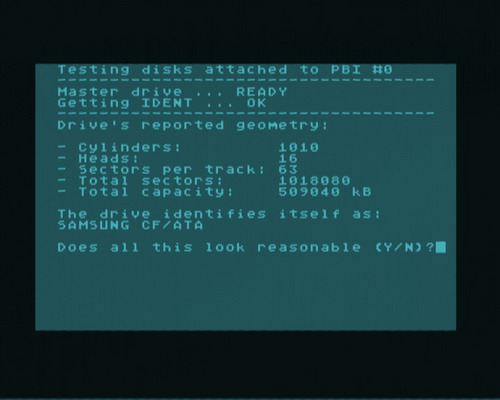

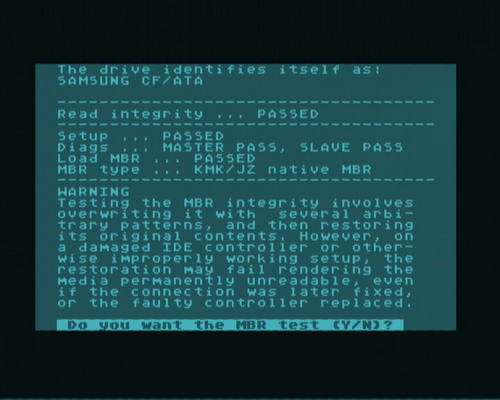

Zrzuty ekranowe z programu IDE DIAG v1.2

Ten artykuł to tylko zalążek. Możesz pomóc rozwojowi Atariki poprzez rozszerzenie go o więcej informacji.