SIMMius 4 MB

From Atariki

(Różnice między wersjami)

| Wersja z dnia 11:58, 13 paź 2012 KMK (Dyskusja | wkład) ← Previous diff |

Wersja z dnia 12:28, 13 mar 2013 KMK (Dyskusja | wkład) Next diff → |

||

| Linia 1: | Linia 1: | ||

| {{grafr|simmius.png}} | {{grafr|simmius.png}} | ||

| - | Prototyp rozszerzenia pamięci zbudowany na 1 module SIMM o pojemności 4MB i zawierający: | + | Prototyp rozszerzenia pamięci zbudowany na 1 module SIMM o pojemności 4 MB i zawierający: |

| - | * [[pamięć liniowa|Pamięć liniową]] 2048kB ($000000...$1FFFFF) dla procesora [[65C816]] | + | * [[pamięć liniowa|Pamięć liniową]] 2048 KB ($000000...$1FFFFF) dla procesora [[65C816]] |

| * Pamięc bankowaną, konfigurowaną programowo, przy użyciu 3 młodszych bitów nieulotnego, 5-bitowego rejestru konfiguracyjnego I2C, jako: | * Pamięc bankowaną, konfigurowaną programowo, przy użyciu 3 młodszych bitów nieulotnego, 5-bitowego rejestru konfiguracyjnego I2C, jako: | ||

| **xx000: bez rozszerzenia | **xx000: bez rozszerzenia | ||

| - | **xx001: 64kB (przełączanie banków bitami PB2,PB3, niezależny dostęp CPU i ANTIC) | + | **xx001: 64 KB (przełączanie banków bitami PB2,PB3, niezależny dostęp CPU i ANTIC) |

| - | **xx010: 128kB (PB2,PB3,PB6, niezależny dostęp CPU i ANTIC) | + | **xx010: 128 KB (PB2,PB3,PB6, niezależny dostęp CPU i ANTIC) |

| - | **xx011: 192kB (PB2,PB3,PB5,PB6) | + | **xx011: 192 KB (PB2,PB3,PB5,PB6) |

| - | **xx100: 256kB (PB2,PB3,PB5,PB6) | + | **xx100: 256 KB (PB2,PB3,PB5,PB6) |

| - | **xx101: 512kB (PB1,PB2,PB3,PB6,PB7, niezależny dostęp CPU i ANTIC) | + | **xx101: 512 KB (PB1,PB2,PB3,PB6,PB7, niezależny dostęp CPU i ANTIC) |

| - | **xx110: 1024kB (PB1,PB2,PB3,PB5,PB6,PB7) | + | **xx110: 1024 KB (PB1,PB2,PB3,PB5,PB6,PB7) |

| - | **xx111: 1984kB (Axlon, 124 banki, $01...$7C) | + | **xx111: 1984 KB ([[Axlon]], 124 banki, $01...$7C) |

| * Pamięć FLASH, zawierającą 4 systemy operacyjne, w tym 3 dostepne do zaprogramowania przez użytkownika, przełączane dwoma starszymi bitami rejestru konfiguracyjnego. | * Pamięć FLASH, zawierającą 4 systemy operacyjne, w tym 3 dostepne do zaprogramowania przez użytkownika, przełączane dwoma starszymi bitami rejestru konfiguracyjnego. | ||

| * Układ sterowania pamięci DRAM zastępujący układ FREDDIE i zapewniający odświeżanie bez ograniczenia liczbą cykli generowanych przez ANTIC. | * Układ sterowania pamięci DRAM zastępujący układ FREDDIE i zapewniający odświeżanie bez ograniczenia liczbą cykli generowanych przez ANTIC. | ||

Wersja z dnia 12:28, 13 mar 2013

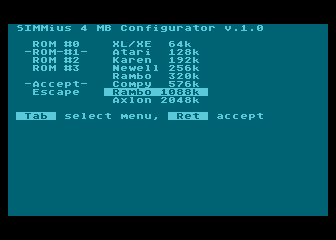

Prototyp rozszerzenia pamięci zbudowany na 1 module SIMM o pojemności 4 MB i zawierający:

- Pamięć liniową 2048 KB ($000000...$1FFFFF) dla procesora 65C816

- Pamięc bankowaną, konfigurowaną programowo, przy użyciu 3 młodszych bitów nieulotnego, 5-bitowego rejestru konfiguracyjnego I2C, jako:

- xx000: bez rozszerzenia

- xx001: 64 KB (przełączanie banków bitami PB2,PB3, niezależny dostęp CPU i ANTIC)

- xx010: 128 KB (PB2,PB3,PB6, niezależny dostęp CPU i ANTIC)

- xx011: 192 KB (PB2,PB3,PB5,PB6)

- xx100: 256 KB (PB2,PB3,PB5,PB6)

- xx101: 512 KB (PB1,PB2,PB3,PB6,PB7, niezależny dostęp CPU i ANTIC)

- xx110: 1024 KB (PB1,PB2,PB3,PB5,PB6,PB7)

- xx111: 1984 KB (Axlon, 124 banki, $01...$7C)

- Pamięć FLASH, zawierającą 4 systemy operacyjne, w tym 3 dostepne do zaprogramowania przez użytkownika, przełączane dwoma starszymi bitami rejestru konfiguracyjnego.

- Układ sterowania pamięci DRAM zastępujący układ FREDDIE i zapewniający odświeżanie bez ograniczenia liczbą cykli generowanych przez ANTIC.

- Przełącznik forsujący niski stan na wszystkich wyjściach rejestru konfiguracyjnego, co pozwala na przywrócenie systemu po błędnym programowaniu pamięci FLASH.

Konstrukcja umożliwia użycie do przełączania banków także bitu PB0, dając dostęp do maksymalnie 128 banków, ale ostatecznie nie zostało to wykorzystane.

Nazwa została zaproponowana przez KMK, zarazem właściciela jedynego egzemplarza komputera z tym rozszerzeniem.