F7

From Atariki

(Różnice między wersjami)

| Wersja z dnia 17:13, 13 lut 2014 Voy (Dyskusja | wkład) (Literówki, przecinki; poprawa 'screenshot' na 'zrzut ekranu') ← Previous diff |

Wersja z dnia 17:14, 13 lut 2014 Voy (Dyskusja | wkład) (jeszcze jeden przecinek :)) Next diff → |

||

| Linia 2: | Linia 2: | ||

| Opracowane przez [[Pasiu|Pasia]]/[[SSG]] (wiosna 2006) rozszerzenie do Atari [[XL]]/[[XE]] oparte na procesorze [[65C816]] pracującym z częstotliwością 14 MHz. Inspiracją jest [[HyperSpeed XL/XE]]. | Opracowane przez [[Pasiu|Pasia]]/[[SSG]] (wiosna 2006) rozszerzenie do Atari [[XL]]/[[XE]] oparte na procesorze [[65C816]] pracującym z częstotliwością 14 MHz. Inspiracją jest [[HyperSpeed XL/XE]]. | ||

| - | Project F7 to system dwuprocesorowy, gdzie 65C816 może pracować równolegle z [[6502C]]. Podobnie jak w [[Warp4]] dostępne jest 512k (lub 1 MB) szybkiej pamięci taktowanej zegarem 14 MHz, a dodatkowo 64k pracującego z tą samą częstotliwością cache'u, zapewniającego szybki odczyt ze "starego" obszaru pierwszych 64k. | + | Project F7 to system dwuprocesorowy, gdzie 65C816 może pracować równolegle z [[6502C]]. Podobnie jak w [[Warp4]], dostępne jest 512k (lub 1 MB) szybkiej pamięci taktowanej zegarem 14 MHz, a dodatkowo 64k pracującego z tą samą częstotliwością cache'u, zapewniającego szybki odczyt ze "starego" obszaru pierwszych 64k. |

| Obok zrzut ekranu z [[SysInfo]] pokazujący parametry prototypowej instalacji. Powstały dwa prototypy; z tego, co wiadomo, oba uległy zniszczeniu. Projekt wyewoluował do rozszerzenia [[Rapidus accelerator]]. | Obok zrzut ekranu z [[SysInfo]] pokazujący parametry prototypowej instalacji. Powstały dwa prototypy; z tego, co wiadomo, oba uległy zniszczeniu. Projekt wyewoluował do rozszerzenia [[Rapidus accelerator]]. | ||

Wersja z dnia 17:14, 13 lut 2014

Opracowane przez Pasia/SSG (wiosna 2006) rozszerzenie do Atari XL/XE oparte na procesorze 65C816 pracującym z częstotliwością 14 MHz. Inspiracją jest HyperSpeed XL/XE.

Project F7 to system dwuprocesorowy, gdzie 65C816 może pracować równolegle z 6502C. Podobnie jak w Warp4, dostępne jest 512k (lub 1 MB) szybkiej pamięci taktowanej zegarem 14 MHz, a dodatkowo 64k pracującego z tą samą częstotliwością cache'u, zapewniającego szybki odczyt ze "starego" obszaru pierwszych 64k.

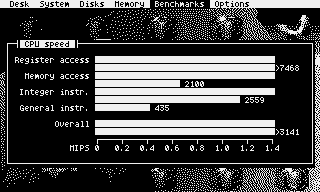

Obok zrzut ekranu z SysInfo pokazujący parametry prototypowej instalacji. Powstały dwa prototypy; z tego, co wiadomo, oba uległy zniszczeniu. Projekt wyewoluował do rozszerzenia Rapidus accelerator.