65C816

From Atariki

65C816 to 16-bitowy następca układu MOS 6502, można nim zastąpić zastosowany w Atari procesor 6502C. 65C816 zaprojektowany został przez Williama D. Menscha jako wersja rozwojowa i następca procesora 65C02. Produkowany jest przez Western Design Center.

Spis treści |

Architektura

- ośmiobitowa szyna danych

- 24-bitowa szyna adresowa

- 92 rozkazy

- 22 tryby adresowania

- 16-bitowe ALU

- jeden 16-bitowy rejestr ogólnego przeznaczenia (akumulator A/B, czyli C)

- dwa szesnastobitowe rejestry indeksowe (X i Y)

- szesnastobitowy wskaźnik strony zerowej - D

- szesnastobitowy wskaźnik stosu - S

- dziewięciobitowy rejestr statusu - P

- dwa ośmiobitowe rejestry adresowe banku programu i danych (K i B)

- szesnastobitowy licznik programu - PC (razem z rejestrem banku programu stanowi 24-bitowy adres)

- wsparcie dla zewnętrznego MMU

- rozkazy przesłań blokowych

- dwa tryby pracy: natywny oraz tryb emulacji 6502 (w tym ostanim procesor się "budzi" po włączeniu zasilania i resecie)

W trybie emulacji 6502 działają wszystkie rozkazy i tryby adresowania 65C816, nie da się jedynie skorzystać z 16-bitowych rejestrów. Dodatkową różnicą jest działanie trybów adresowania indeksowanych strony zerowej: jeśli adres wynikający z dodania adresu bazowego i rejestru indeksowego jest większy niż 255, w trybie emulacji 6502 "zawija się" on do początku strony zerowej, natomiast w trybie natywnym adres efektywny wskaże obszar poza stroną zerową. Żeby było dowcipniej, zachowanie takie w trybie emulacji dotyczy tylko rozkazów 6502, ale nie 65C02 - dlatego w trybie emulacji 6502, gdy rejestr X ma wartość $FF, rozkaz STZ $FF,X zapisze daną pod zupełnie inny adres ($01FE) niż rozkaz STA $FF,X ($00FE).

Osobliwością procesora jest działanie rejestrów C, X i Y: są one 16-bitowe, ale żeby skorzystać z ich pełnego rozmiaru, trzeba oddzielnym rozkazem dokonać przełączenia dodatkowych bitów rejestru statusu. Jeden z nich, zwany M, wybiera rozmiar akumulatora oraz operacji na pamięci (1 - ośmiobitowe, 0 - szesnastobitowe), drugi zwany X ma analogiczne znaczenie dla obydwu rejestrów indeksowych.

Dodatkowo rejestry indeksowe i akumulator zachowują się nieco odmiennie przy manipulacji bitami M i X. Mianowicie przełączenie rejestrów X i Y z szesnastu na osiem bitów zeruje ich starsze bajty, natomiast przełączenie akumulatora na osiem bitów powoduje, że "rozpada się" on na dwie połówki, ale zawartość starszej jest w dalszym ciągu dostępna jako "akumulator B".

Szesnastobitowe rejestry C, X, Y są dostępne tylko w trybie natywnym 65C816, natomiast w trybie emulacji 6502 istnieje dostęp do akumulatora B - obydwie połówki rejestru C można zamienić miejscami.

Rozszerzenia oparte na 65C816

Warp4

Od powyższego, bardziej zaawansowane rozszerzenie to Warp4, autorstwa Pasia/SSG. Warp4 opórcz samego CPU oferuje też nieco (1 MB) pamięci liniowej. Obszar powyżej pierwszych 64k pamięci taktowany jest szybszym zegarem - w zależności od wersji procesora może to być 3,54 lub 7 MHz. "Stare" 64k taktowane jest tradycyjnie, na 1,773 MHz.

Projekt F7

Pasiu pracuje również nad kolejnym rozszerzeniem, dla którego inspiracją jest Hyperspeed XL/XE.

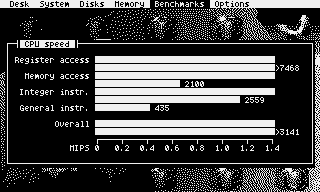

Projekt F7 to system dwuprocesorowy, gdzie 65C816 może pracować równolegle z 6502C. Podobnie jak w Warp4 dostępny jest 1 MB szybkiej pamięci taktowanej zegarem 14 MHz, a dodatkowo 64k pracującego z tą samą częstotliwością cache'u zapewniającego szybki odczyt ze "starego" obszaru pierwszych 64k.

Obok screenshot z SysInfo pokazujący parametry prototypowej instalacji. Zobacz też oficjalną stronę projektu.

Download

Zobacz też

- 65C816 Microprocessor Data Sheet (po angielsku)

- 65C02/65C816 Programming Manual (po angielsku)

- Procesor MOS 65C816 (po polsku)

- DracOS