Programowanie: Pełny 240-liniowy hires

From Atariki

ANTIC potrafi wyrysować na ekranie 240 linii skanningowych począwszy od 8 linii ekranowej do 247 włącznie. Robi to na podstawie Display Listy.

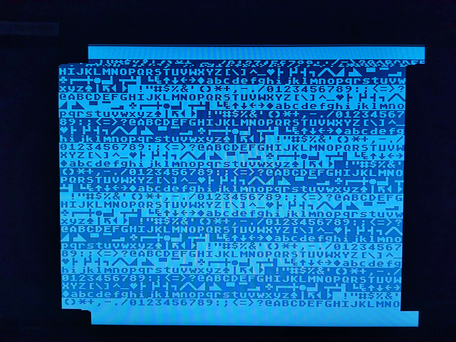

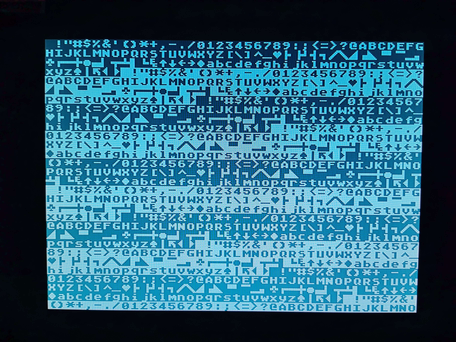

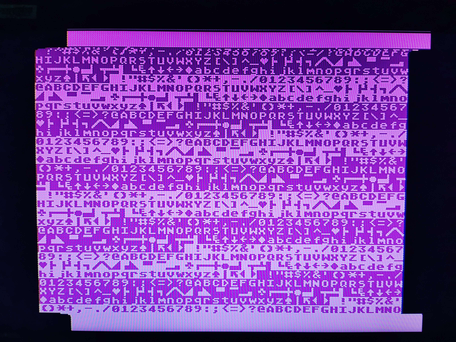

O ile dla trybów kolorowych można wykorzystać pełne 240 linii, o tyle tryby hires (ANTIC 2, ANTIC 3 i ANTIC F), ale również tryby GTIA (Graphics 9, Graphics 10 i Graphics 11) bazowane właśnie na trybie ANTIC F w takim przypadku powodują zerwanie synchronizacji pionowej, przez co prawidłowa lista wyświetlania może składać się z 239 linii i skoku JVB skutkującego wyświetlaniem jednej pustej linii na samym dole ekranu.

dlist:

.byte $0F | $40 ;LMS

.word screen.?part1

:99 .byte $0F

.byte $0F | $40 ;LMS

.word screen.?part2

:99 .byte $0F

.byte $0F | $40 ;LMS

.word screen.?part3

:38 .byte $0F

.byte $41 ;JVB

.word dlist

Sposób na poradzenie sobie z problemem opisał Rybags w wątku Overcoming the Scanline 240 lines "bug": sztuczka polega na wyłączeniu DMA dla ekranu przed końcem linii 247 - ostatniej kreślonej przez ANTIC, po czym przywróceniu go na początku linii 8 - pierwszej rysowanej przez ANTIC.

init:

...

lda #%00100000

ldx #<dlist

ldy #>dlist

sta DMACTLS ;$22F

stx DLPTRS ;$230

sty DLPTRS+1

ldy #<vbint

ldx #>vbint

lda #VBLKD ;7

jsr JSETVBV ;$E45C

ldy #<dlint

ldx #>dlint

lda #%11000000

sty VDSLST ;$200

stx VDSLST+1

sta NMIEN ;$D40E

...

vbint:

lda #8/2

?w cmp VCOUNT ;$D40B

bne ?w

lda #%00100010

sta DMACTL ;$D400

jmp JEXITVB ;$E462

dlint:

pha

lda #%00100000

sta WSYNC ;$D40A

sta DMACTL ;$D400

pla

rti

dlist:

.byte $02 | $40 ;LMS

.word screen

:28 .byte $02

.byte $02 | $80 ;DLI

; .byte $41 ;JVB

; .word dlist

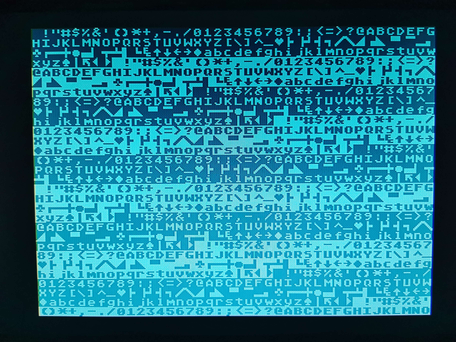

W powyższym przykładzie:

- do uzyskania 240 lini hires wykorzystano 30 wierszy trybu ANTIC 2 (30*8=240),

- do wyłączenia DMA ekranu używane jest przerwanie DLI w ostatnim wierszu ekranu (zajmującego linie 240-247, a zgłaszającego DLI w linii 247),

- a do przywrócenia DMA ekranu przerwanie VBL (a konkretnie opóźniona faza procedury obsługi przerwania VBLK).

Warto zwrócić uwagę na to, że w DMACTLS (czyli cieniu DMACTL) DMA dla ekranu jest wyłączone (bity 0 i 1 równe %00) a to z tego powodu, że przed wykonaniem opóźnionej fazy VBLK rejestry ANTIC-a (między innymi DMACTL i DLPTR) są ustawiane na podstawie rejestrów-cieni, zaś włączenie DMA ekranu przed linią 8 spowoduje zerwanie synchronizacji (VBLK zgłaszane jest przez ANTIC w 248 linii skanningowej).

Ostatni skok JVB w Display List jest zbędny ponieważ w międzyczasie na przerwaniu VBLK zostaje ustawiona nowa wartość DLPTR i ANTIC rozkazu JVB już nie czyta.